Gowin Entwicklungsumgebung

SiPeed hat ein Entwicklungsboard mit einem Gowin GW1NSR-LV4C FPGA vorgestellt. Das "Tang Nano 4K" Board ist bei Aliexpress um €19 erhältlich. Diese sogenannten LittleBee FPGAs vereinen FPGA, Flash, SDRAM und einen ARM uC in einem Gehäuse. Noch dazu sind QFP Gehäuse verfügbar, die auch einfach händisch gelötet werden könnten.

Ich entschied mich mithilfe dieses Entwicklungsboards ein erstes FPGA Projekt umzusetzen.

Die Idee war, durch das integrierte SDRAM ein EPROM zu emulieren, das dann die Spielekasette eines Gameboys ersetzen könne.

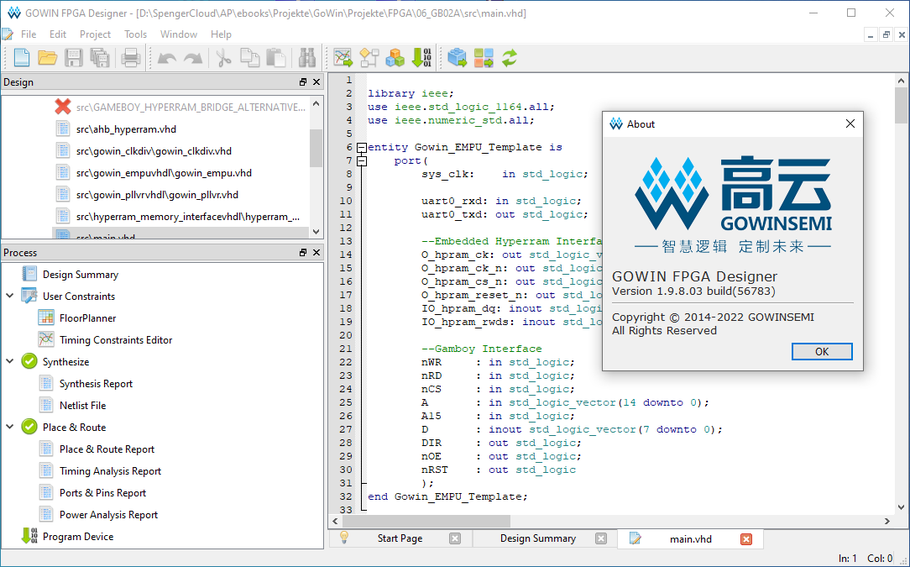

Gowin stellt zudem eine Entwicklungsumgebung zur Verfügung, die in der Educational Version das am Entwicklungsboard verwendete Bauteil unterstützt. Es wird auch eine Lizenz für die Vollversion auf Anfrage gratis zur Verfügung gestellt.

Die Entwicklungsumgebung unterstützt sowohl Verilog als auch VHDL. Die integrierten Module sind in Verilog geschrieben, lassen sich aber problemlos mit VHDL kombinieren.

Das SiPeed Tang Nano 4K Board enthält eine Programmierschnittstelle, die anscheinend nicht zu 100% mit dem original Programmiergerät von Gowin kompatibel ist. Deshalb wird auf der SiPeed Homepage eine kompatible Programmier-Software zum Download angeboten.

Für den Hard Core Processor wird ebenfalls eine Educational Entwicklungsumgebung angeboten.

Schaltplan

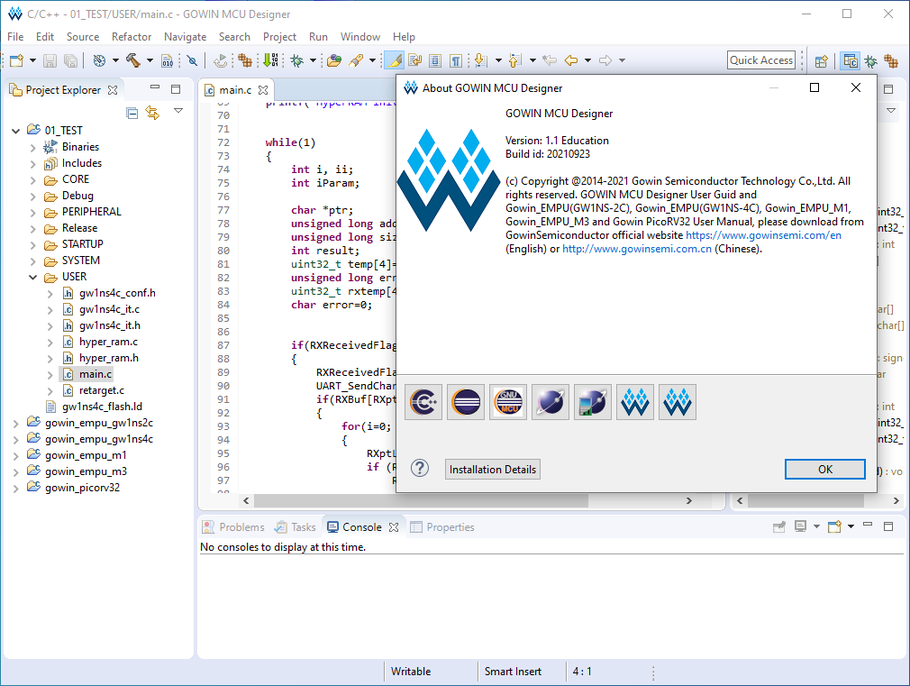

Um das FPGA Board an den Gameboy anzubinden musste eine Leiterplatte designt werden, die mechanisch die Signale des Gameboy-Einschubs abgreifen kann, und die 5V Signale des Gameboys entsprechend konvertiert.

Ich musste einige Lösungen verwerfen, bis ich einen idealen Baustein für die Pegelwandlung gefunden hatte.

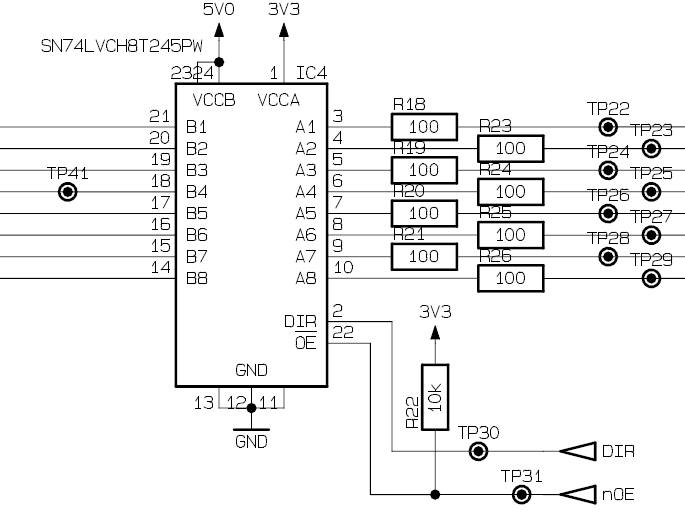

Die Aufgabe wird von 74LVCH8T245 Bausteinen übernommen. Sie besitzen 2 Spannungsversorgungen, um digitale Signale zwischen beliebigen Versorgungsspannungen zu konvertieren, sind bidirektional und haben eine BusHold-Funktion integriert.

Wenn der Datenbus des Gameboys in einen hochohmigen Zustand schaltet, ziehen integrierte Pull-Ups die Signale nach +5V. Diese Flanken sind aber sehr langsam, sodass die maximale Transition Time von CMOS Eingängen überschritten wird, was zu Oszillationen oder erhöhten Strombedarf führen kann. Eine Abhilfe wären Schmitt-Trigger Eingänge, die ebenfalls keine Probleme mit langsamen Flanken haben. Eine andere Möglichkeit ist eine Bus-Hold Funktion, die den Pegel auf einem definierten Zustand haltet, auch wenn gerade niemand aktiv den Bus treibt.

Das Board wurde bei JLCPCB gefertigt und mit einer HotPlate gelötet.

FPGA Project Files

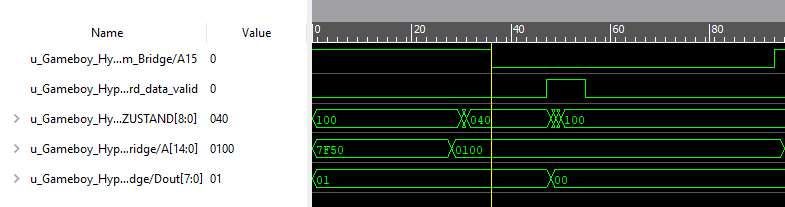

Die Hauptaufgabe des FPGAs liegt darin, die Adresse des parallelen Adressbusses vom Gameboy einzulesen, die Daten dieser Adresse vom internen SDRAM über dessen Schnittstelle auszulesen und bei aktivem CS Signal des Gameboys, die Daten auf den parallelen Datenbus auszugeben.

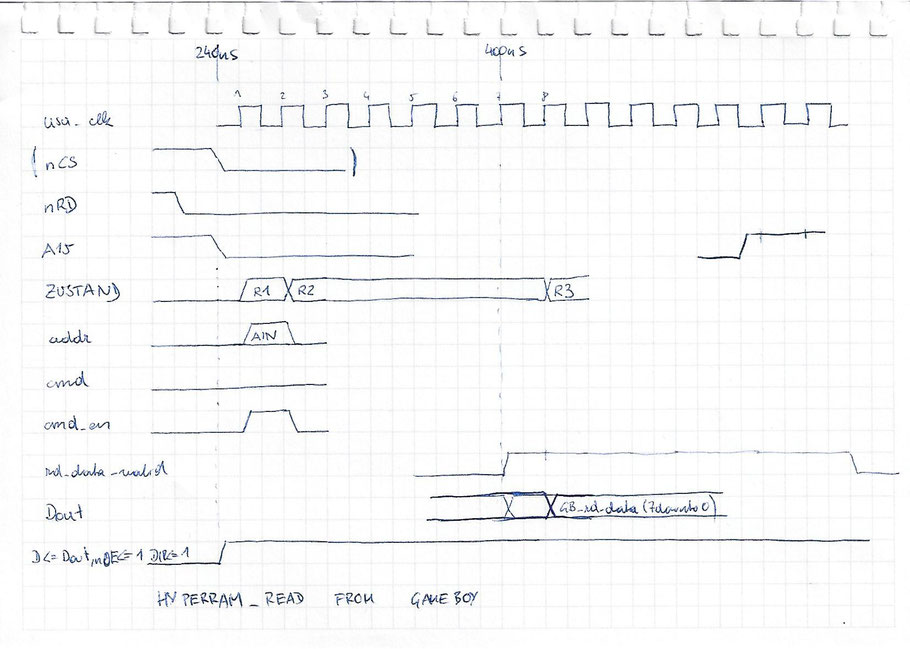

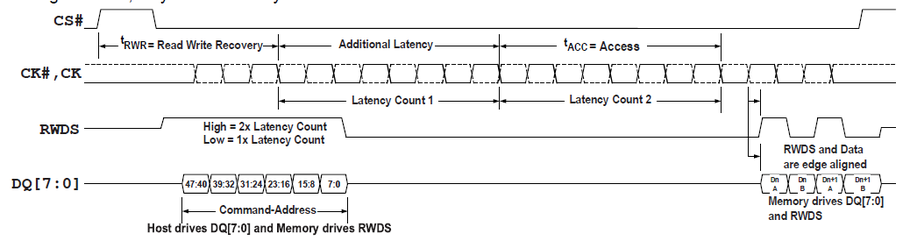

Die Skizze zeigt das Timing-Diagram für das Lesen des SDRAMS über den Gameboy.

A15 dient als CS Signal.

Die user_clk im FPGA, über die das SDRAM angesprochen wird, kann mit max. 80 MHz betrieben werden.

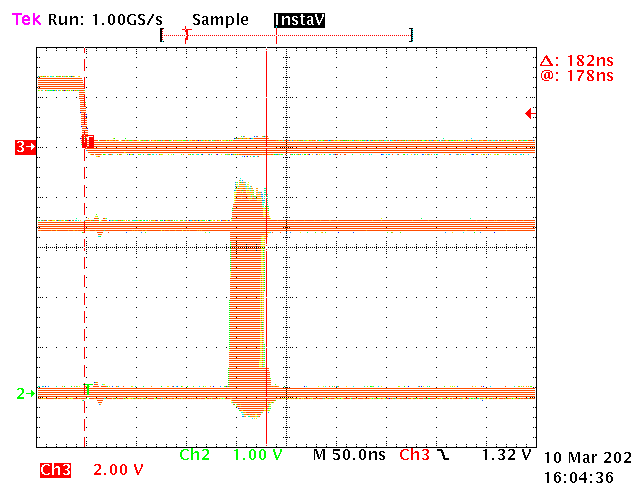

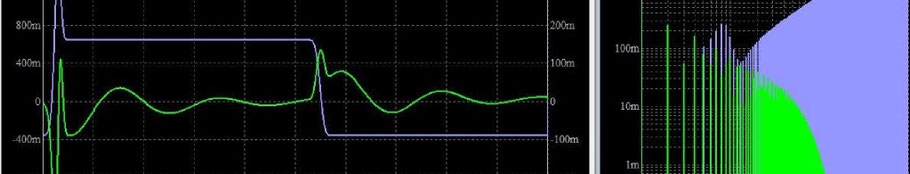

Der Knackpunkt ist die Zeit, die benötigt wird, das interne SDRAM zu lesen. Eine Messung zeigt, dass spätestens 182ns nach der fallenden Flanke des CS Signals, die Daten auf dem Bus liegen.

ARM Firmware

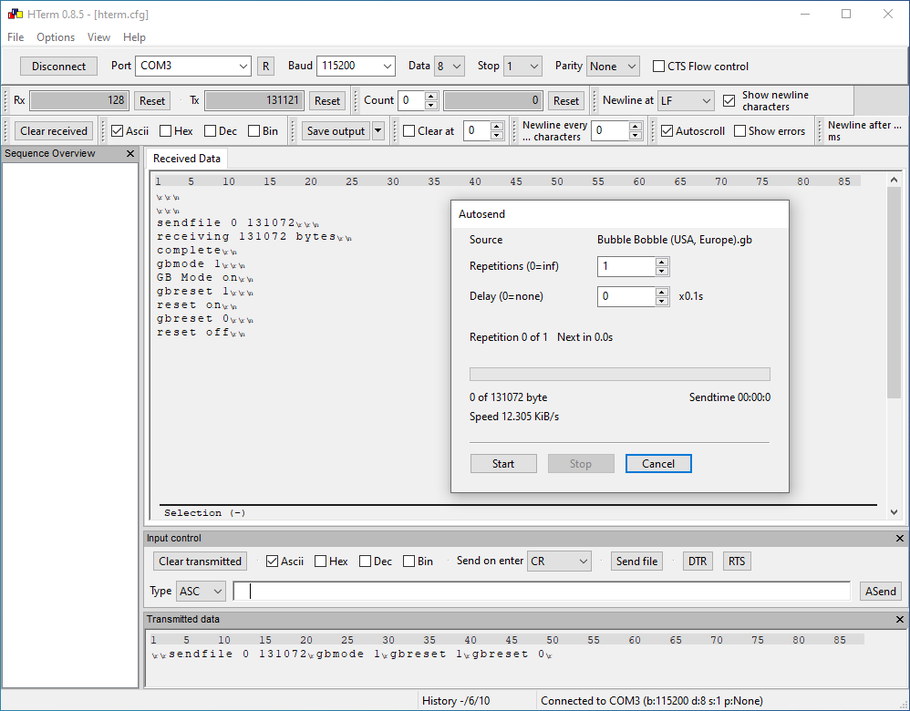

Die Aufgabe der Firmware ist es, die Binärdaten des Spiels über die serielle Schnittstelle einzulesen und in das SDRAM zu schreiben. Über die Firmware wird auch das Resetsignal des Gameboys gesteuert.

Ich benutze HTerm um über einen USB-RS232 Adapter mit dem FPGA zu kommunizieren.

Grundsätzlich funktioniert das ganze zwar, aber bei einigen Spielen zeigen sich Probleme, in dem sie entweder nicht starten, oder während des Spielens abstürzen.

Es zeigte sich, dass das Timing relativ knapp ist.

Es ist aus den verfügbaren Unterlagen nicht zu erkennen, wann die Daten vom Gameboy eingelesen werden. Wenn ich das Auslesen der Daten mit der fallenden /CS Flanke triggere, werden die Daten am Datenbus nach meinen Versuchen zu spät angelegt.

Um die Daten früher anlegen zu können, triggere ich das Auslesen des SDRAMS bereits bei Änderung des Adressbusses, und nicht erst bei der Flanke des /CS-Signals (A15 wird als /CS verwendet).

Wenn ich den internen Takt des FPGAs etwas verlangsame, sodass die Daten etwas später am Datenbus anliegen, sind die Spiele nicht mehr lauffähig. Bereits das Gameboylogo beim Start wird fehlerhaft angezeigt. Allerdings sehe ich bei diesem Konzept keine Möglichkeit mehr, das interne SDRAM schneller auszulesen. Die sogenannte HyperRAM Schnittestelle des SDRAMS benötigt nämlich 14 Takte, bis die Daten gelesen werden können.

Write a comment